#### Field Programmable Gate Array (FPGA) Curriculum update with Industry

Hosted by MATEC NetWorks

National Science Foundation

Funded, in part by a grant from the National Science Foundation DUE 1003542

E

| eventarininate enventaria versinaria |          |

|--------------------------------------|----------|

| File Session View Tools Window Help  |          |

|                                      | Chat Box |

|                                      |          |

11

C Participants

🖑 🗚 🖖 🚳 🦯 🗖 Participants

| ₩ <mark>₩</mark><br>6 € | 1<br>Participant |   |

|-------------------------|------------------|---|

| E) Chat                 |                  |   |

| ihow All                |                  | - |

🕕 🚯 🖌 🗖 Mark Viguesney (Moderator, Me)

#### **Chat Box**

#### Type Comment Here

In the **Chat Box**, please type the name of your school or organization, your location, and how many people are attending with you today.

Elluminate Live! - NetWorks Webinars

File Session View Tools Window Help

🖑 👫 🕕 🚳 🦯 🗖 Participants

C Participants

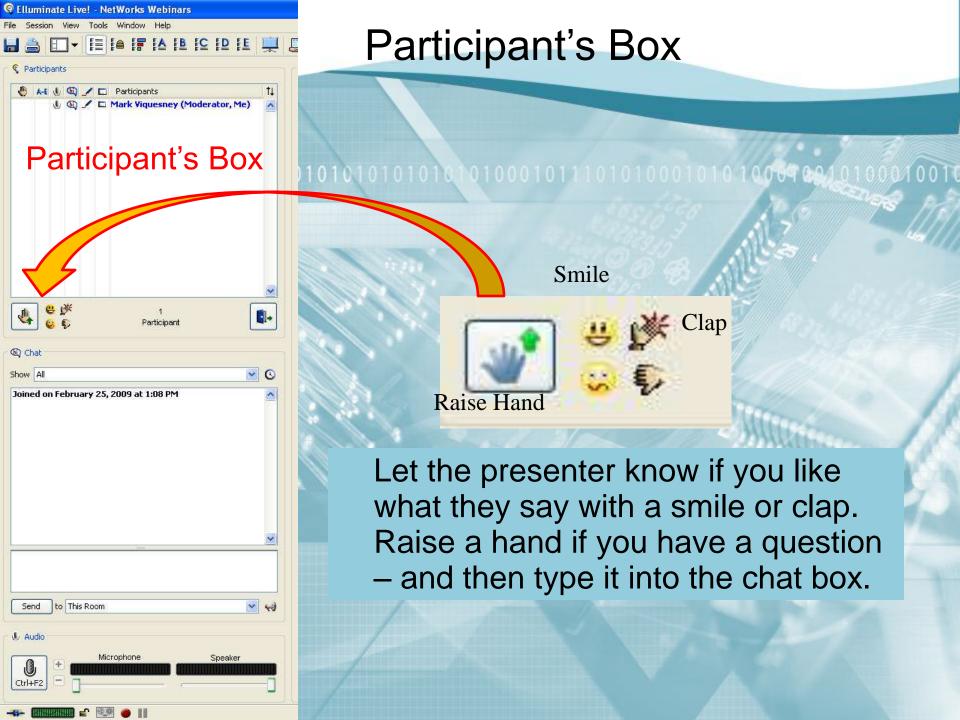

#### Participant's Box

#### Participant's Box

🖖 🚯 🖌 🗖 Mark Viquesney (Moderator, Me)

11

| ●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | 1<br>Participant  |          |

|------------------------------------------------|-------------------|----------|

| ow All                                         | , 2009 at 1:08 PM | ✓ C      |

|                                                |                   | <u> </u> |

| Send to This Room                              |                   | ₩ ₩      |

| Audio                                          | crophone          | Speaker  |

### Allows you to non-verbally respond to the presenter's comments.

| S Elluminate Live! - NetWorks Webinars  |                                  |

|-----------------------------------------|----------------------------------|

| File Session View Tools Window Help     |                                  |

|                                         | 11 💻 🛛                           |

| 🔇 Participants                          |                                  |

| 🕘 👫 🕖 🚳 🦯 🗖 Participants                | t1                               |

| ال الله الله الله الله الله الله الله ا |                                  |

| e j 1<br>S S Participant                |                                  |

|                                         |                                  |

| Chat                                    |                                  |

| Show All                                | <b>V</b> O                       |

| Joined on February 25, 2009 at 1:08 PM  |                                  |

|                                         |                                  |

|                                         | <u> </u>                         |

|                                         |                                  |

|                                         |                                  |

| Send to This Room                       | <ul> <li>✓</li> <li>✓</li> </ul> |

| L Auda                                  |                                  |

| Microphone Speake                       | er                               |

|                                         | Ē                                |

|                                         |                                  |

#### Click A-E to take the Poll

Poll

This webinar will have a Poll. Please answer: I heard about this webinar through:

A. @matec

- B. Email from ETD list serv

- C. Email from HTWI

- D. Friend or colleague

- E. Other (please type where in chat box)

#### eSyst Webinar Presenters

#### Bassam Matar

HTWI

High Tech Workforce Initiative

Engineering Faculty and Program Coordinator at Chandler/Gilbert C.C.

#### **Ui Luu** Electronics Faculty Glendale C.C.

#### Field Programmable Gate Array (FPGAs) Curriculum Validation with Industry Agenda

- Overview of the existing course offerings at MCCCD.

- Overview of the externship with local industry

- Curriculum Update

- Xilinx Workshop

- Summer 2011 Workshop

- Survey and Final Questions from Participants

#### **HTWI Project Team Members**

HT

High Tech Workforce Initiative

**Rick Hansen– Principal Investigator**

Lizette Acosta - Coordinator Marketing & Academic Advisement

# **HTWI Project Overview**

HTWI

High Tech Workforce Initiative

# Faculty work side by side with industry to design, develop and deliver this curriculum.

# HTWI Project Overview (cont.)

AND STREET

HTWI

High Tech Workforce Initiative

Research industry requirements and provide students with a relevant, rigorous and interdisciplinary course of study

# HTWI Project Overview (cont.)

HTWI

High Tech Workforce Initiative

Reform curriculum and delivery to meet industry requirements and provide students with a relevant, rigorous and interdisciplinary course of study

# HTWI Project Overview (cont.)

High Tech Workforce Initiative

3) Redefine Maricopa Colleges' outreach and retention strategies to attract more students into the high-tech manufacturing fields to meet future employment demands

#### Electronics and Engineering Courses HIWI High Tech Workforce Initiative

- Digital Design Fundamentals (CSC/EEE 120)

- Introduction to Digital Logic (ELT 131)

- Microprocessor Applications inc. Microcontrollers (CSC/EEE 230 or ELT 241

#### Electronics and Engineering Courses HIWI High Tech Workforce Initiative

Our existing courses have been focused on Transistor-Transistor-Logic (TTL).

As a result of an externship in the Summer of 2009 we started implementing Field Programmable Gate Array (FPGA) using Schematics captures.

#### Externship with Local Industry HTWI High Tech Workforce Initiative

In phase 1 of this project, we consulted with Honeywell & General Dynamics on FPGAs in industrial use

Our initial findings: Very (High Speed Integrated Circuits) Hardware Description Language (VHDL)

The growing trend in Digital Design is to adapt Verilog as a new design tool.

# Externship with Local Industry (cont.)HTWI

After review we concluded the existing digital course curriculum requires

- more coverage in VHDL

- less with Schematic Capture

Xilinx software works better with VHDL programming than Schematic Capture.

### **Action Plan**

This gap analysis prompts us to:

- Attend FPGA/VHDL workshop sponsored by Xilinx.

- If future externship opportunity exists, we will work with our industrial partner to develop further Verilog updates.

2. Update our Digital Design curriculum to increase coverage in VHDL.

#### **General Lecture Recommendation**

HTWI High Tech Workforce Initiative

The following subjects should be added to a Digital course or more detailed coverage should be included:

- Increased coverage of PLDs.

- Basic programming techniques in VHDL, Verilog or an equivalent language should be introduced.

Rationale: A large percentage of new digital designs use a PLD and students must be familiar with the basic types, inputs, outputs, specifications, and architectures. Students must know how to access inputs and outputs and assess functionality.

#### General Lab Recommendation HTWI High Tech Workforce Initiation

- Less breadboarding with discrete TTL or CMOS logic.

- Add significant PLD coverage that can be programmed as well as including an Altera or Xilinx student demo board with

- prebuilt I/O devices (switches, LEDs, LDC display, etc)

- multiple common interfaces

- ex: FPGA Spartan 3E, Nexys2 FPGA Board

- Add activities that allow students to practice test and measurement techniques and troubleshooting. Add a logic analyzer to the lab as budget permits.

### General Textbook Recommendation HTWI

- Use the existing textbook but edit the content to avoid or de-emphasize the topics discussed previously and to enhance the suggested topics.

- Search for supplementary material on the Internet and other sources to cover topics not adequately covered in the textbooks.

- Change to a textbook that incorporates the most recent techniques

- ex: PLDs and microcontrollers.

Sample reference book: Digital Fundamentals with VHDL by Floyd

####

Sec.

# **Questions?**

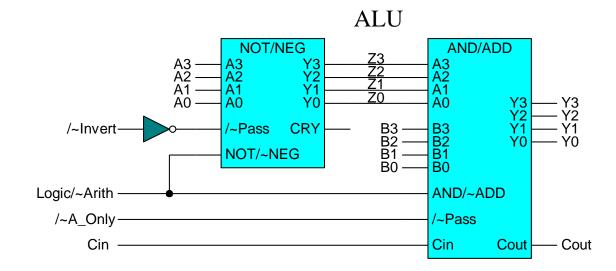

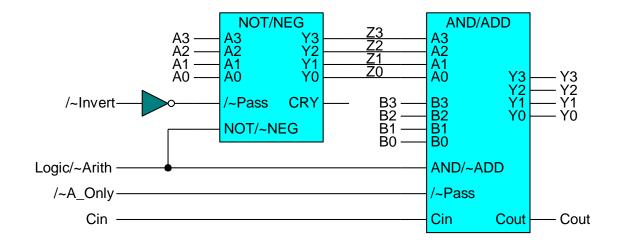

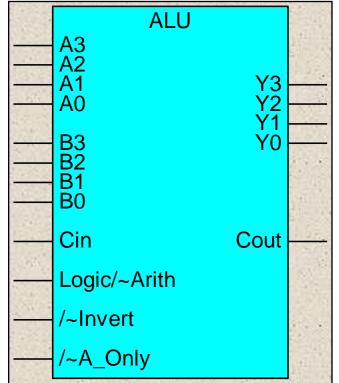

Arithmetic Logic Unit (ALU) Lecture with VHDL

By Bassam Matar

Security System Design Lab with VHDL By Ui Luu

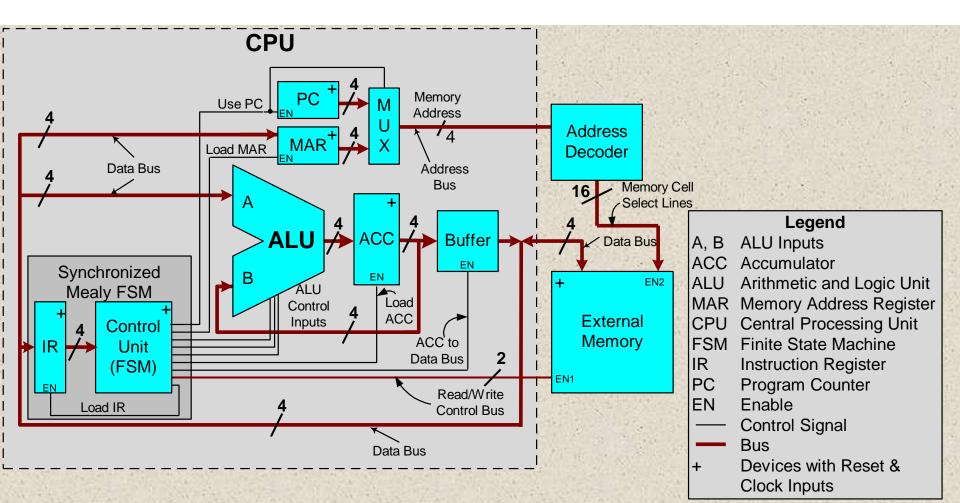

# Arithmetic Logic Unit (ALU)

## Design and Build an ALU with Schematic Capture and VHDL

- Let's talk about Arithmetic and Logic Unit's (ALU's.)

- A microprocessor is made up of many components:

- Central Processing Unit Performs the data manipulation tasks of the computer and sequences each step in these tasks.

- Arithmetic and Logic Unit (ALU) is the part of the CPU which does the arithmetic (+,-,\*,etc.) and the logical operations (AND, OR, NOT etc.).

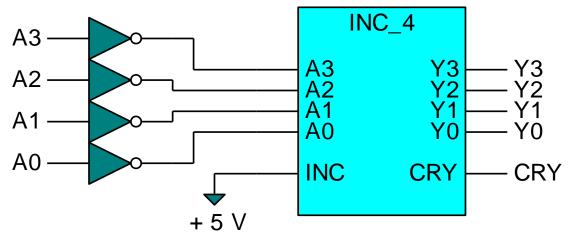

- Each ALU has a different design. Lets look at the one you're building in simulation lab 3.

- You already took the first step in the ALU design. In Sim Lab 1 you built the circuit that does the two's complement operation.

AND/~ADD-

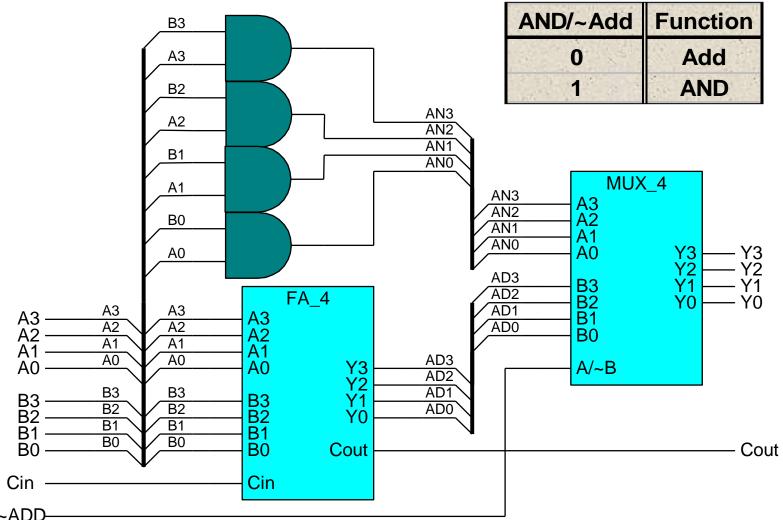

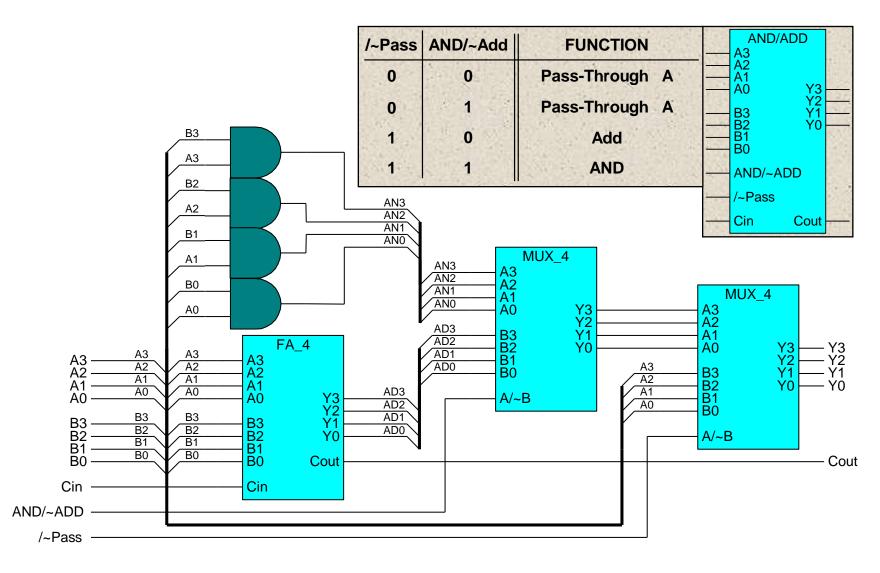

#### AND/ADD Circuit w/ Pass-Through

TEAMS: Fill in the function definition table below for the ALU.

| A<br>ONLY' | ARITH'/LOGIC | INVERT | FUNCTION              | HEX<br>INPUT A | HEX<br>INPUT B | HEX<br>OUTPUT |

|------------|--------------|--------|-----------------------|----------------|----------------|---------------|

| 0          | 0            | 0      | PASS-THROUGH          | E              | D              | Е             |

| 0          | 0            | 1      | 2's COMPLIMENT of A   | C              | Е              | 4             |

| 0          | 1            | 0      | PASS-THROUGH          | F              | 9              | F             |

| 0          | 1            | 1      | 1's COMP of A         | F              | С              | 0             |

| 1          | 0            | 0      | A plus B              | 2              | 5              | 7             |

| 1          | 0            | 1      | (2's COMP A) plus B   | F              | А              | В             |

| 1          | 1            | 0      | A AND B               | F              | 8              | F             |

| 1          | 1            | 1      | (1's COMP of A) AND B | 2              | 5              | D             |

#### Top Level VHDL Programming of ALU's

| A<br>ONLY' | ARITH'/LOGIC | INVERT | FUNCTION              | HEX<br>INPUT A | HEX<br>INPUT B | HEX<br>OUTPUT |

|------------|--------------|--------|-----------------------|----------------|----------------|---------------|

| 0          | 0            | 0      | PASS-THROUGH          | E              | D              | E             |

| 0          | 0            | 1      | 2's COMPLIMENT of A   | С              | Е              | 4             |

| 0          | 1            | 0      | PASS-THROUGH          | F              | 9              | F             |

| 0          | 1            | 1      | 1's COMP of A         | F              | С              | 0             |

| 1          | 0            | 0      | A plus B              | 2              | 5              | 7             |

| 1          | 0            | 1      | (2's COMP A) plus B   | F              | А              | В             |

| 1          | 1            | 0      | A AND B               | F              | 8              | F             |

| 1          | 1            | 1      | (1's COMP of A) AND B | 2              | 5              | D             |

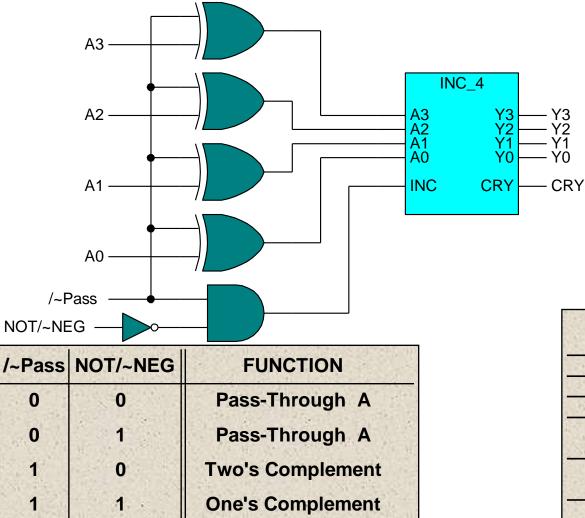

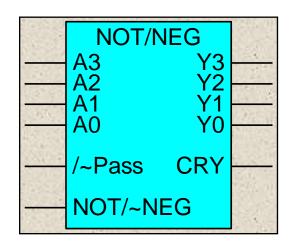

# <u>NEG\_NOT</u> VHDL Component Programming of ALU's

| /~Pass | NOT/~NEG | FUNCTION         |

|--------|----------|------------------|

| 0      | 0        | Pass-Through A   |

| 0      | 1        | Pass-Through A   |

| 1      | 0        | Two's Complement |

| 1      | 1        | One's Complement |

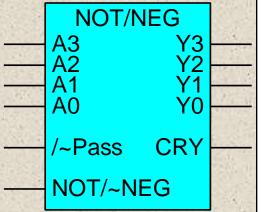

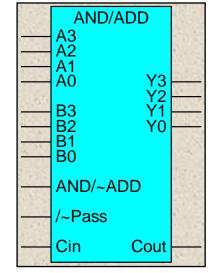

# <u>AND/ADD</u> VHDL Component Programming of ALU's

| /~Pass | AND/~Add | FUNCTION     |          |

|--------|----------|--------------|----------|

| 0      | 0        | Pass-Through | Α        |

| 0      | 1        | Pass-Through | A        |

| 1      | 0        | Add          | THE REAL |

| 1      | 1        | AND          | 1        |

• We need the function definition tables because after the ALU is put in a "box", we need to know how to use it and connect it.

Arithmetic Logic Unit (ALU) Lecture with VHDL

By Bassam Matar

Security System Design Lab with VHDL By Ui Luu

# Security State Machine

## Ui Luu Glendale Community College

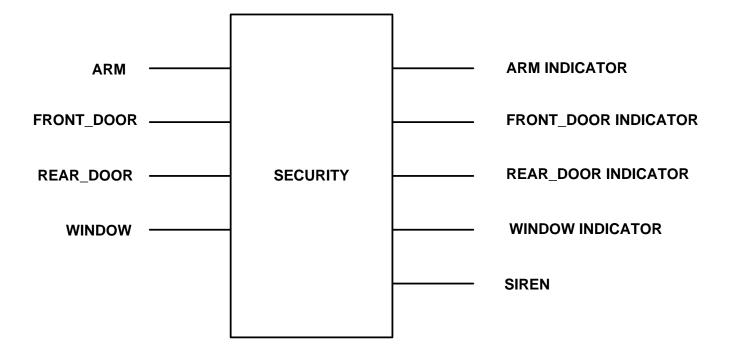

### Security System I/O

Figure 1. Security System I/O

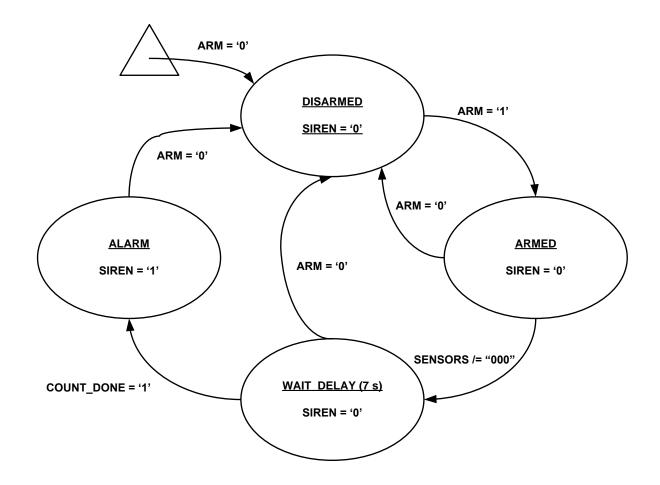

### Security System State Diagram

Figure 2. SECURITY SYSTEM STATE DIAGRAM

## Objectives & Learning Outcomes

After completing this module, you will be able to:

Create a top-level HDL structure

➤Write VHDL code to describe a synchronous state machine diagram

≻Utilize LED\_DRIVER module developed in previous lab for timer display

Create / use a constraint file for pin-out assignments

Download to the SPARTAN 3E demo board for in-circuit verification.

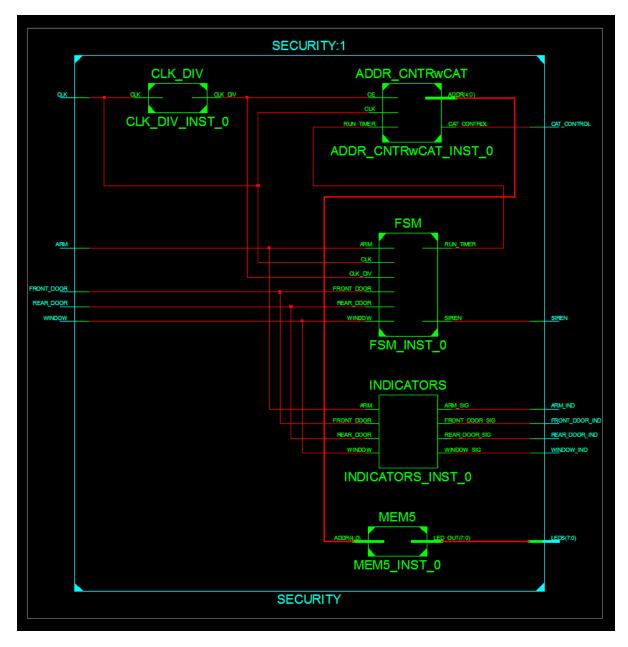

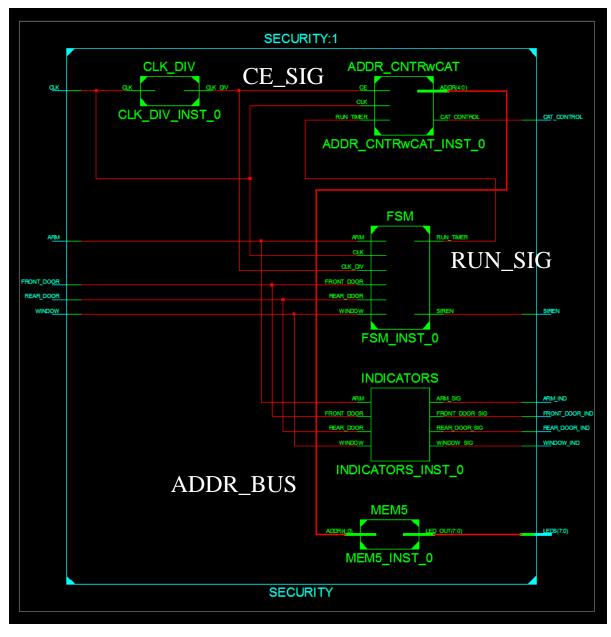

### Security System Block Diagram

#### Creating the Top-Level Module (SECURITY.vhd)

- -- Module Name: SECURITY.vhd

- -- Project Name: Security State Machine

- -- Target Devices: Xilinx Spartan 3E / xc3s500e

- -- Tool versions: Win7 / Xilinx ISE 12.1

- -- Description: Sample solution for Security State Machine

-- \* This is the top level module that pulls together all sub modules

-- \* use LED Drivers developed in previous lab for Timer display

| <br>SECURITY.vhd (this module)                             |

|------------------------------------------------------------|

| <br>* CLK_DIV.vhd (Clock Divider)                          |

| <br>* ADDR_CNTRwCAT.vhd (Address Counter with CAT control) |

| <br>* MEM5.vhd (Memory for 2 digits 7-segment LEDs Display |

| <br>* FSM.vhd (State Machine)                              |

| <br>* INDICATORS.vhd (Onboard LED Indicators)              |

| <br>* SECURITY.ucf (I/O Assignments)                       |

#### Create Entity SECURITY

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

#### entity SECURITY is

port (

CLK : in std\_logic; ARM : in std\_logic; FRONT\_DOOR: in std\_logic; REAR\_DOOR: in std\_logic; WINDOW: in std\_logic; SIREN : out std logic;

```

ARM_IND : out std_logic;

FRONT_DOOR_IND: out std_logic;

REAR_DOOR_IND: out std_logic;

WINDOW_IND: out std_logic;

```

LEDS : out STD\_LOGIC\_VECTOR (7 downto 0); CAT\_CONTROL :out STD\_LOGIC ); end entity SECURITY;

#### Architecture & Components

architecture RTL of SECURITY is

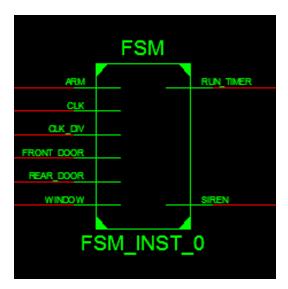

component FSM

Port (

CLK : in STD\_LOGIC; CLK\_DIV:in STD\_LOGIC; ARM : in STD\_LOGIC; FRONT\_DOOR : in STD\_LOGIC; REAR\_DOOR : in STD\_LOGIC; WINDOW : in STD\_LOGIC; RUN\_TIMER:out STD\_LOGIC; SIREN : out STD\_LOGIC);

#### Components CLK\_DIV & MEM5

component CLK\_DIV

Port ( CLK: in STD\_LOGIC;

CLK\_DIV: out STD\_LOGIC);

end component;

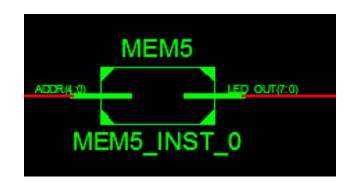

component MEM5

Port ( ADDR: in std\_logic\_vector (4 downto 0); LED\_OUT: out STD\_LOGIC\_VECTOR(7 downto 0));

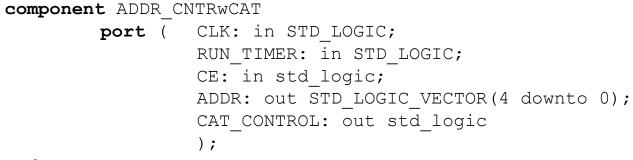

#### Component: ADDR\_CNTRwCAT

#### **Component: INDICATORS**

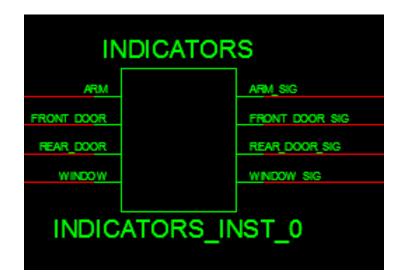

component INDICATORS

Port ( ARM : in STD\_LOGIC;

FRONT\_DOOR : in STD\_LOGIC;

REAR\_DOOR : in STD\_LOGIC;

WINDOW : in STD\_LOGIC;

ARM\_SIG : out STD\_LOGIC; FRONT\_DOOR\_SIG : out STD\_LOGIC; REAR\_DOOR\_SIG : out STD\_LOGIC; WINDOW SIG : out STD\_LOGIC);

#### Signal provides interconnect between Components

signal CE\_SIG: std\_logic;

signal ADDR\_BUS: std\_logic\_vector(4 downto 0);

signal RUN\_SIG: std\_logic;

See System Block Diagram (next slide)

### Signal provides interconnect between Components

#### Create Instance of Component INDICATORS

component INDICATORS Port ( ARM : in STD LOGIC; FRONT DOOR : in STD LOGIC; REAR DOOR : in STD LOGIC; WINDOW : in STD LOGIC; ARM SIG : out STD LOGIC; FRONT DOOR SIG : out STD LOGIC; REAR DOOR SIG : out STD LOGIC; WINDOW SIG : out STD LOGIC); end component; **INDICATORS INST 0:** INDICATORS **port map**( ARM => ARM,FRONT DOOR => FRONT DOOR, REAR DOOR => REAR DOOR , WINDOW => WINDOW, ARM SIG => ARM IND, FRONT DOOR SIG => FRONT\_DOOR\_IND, REAR DOOR SIG => REAR DOOR IND, WINDOW SIG => WINDOW IND );

-- Left hand side includes I/Os at the component ports

-- Right hand side includes signals that the ports are attached to connect to other components

#### Create Instances of Components: CLK\_DIV, ADDR\_CNTRwCAT, MEM5, FSM

CLK DIV\_INST\_0: CLK DIV port map (CLK=>CLK, CLK DIV=>CE SIG);

ADDR\_CNTRwCAT\_INST\_0: ADDR\_CNTRwCAT port map ( CLK=>CLK, RUN\_TIMER => RUN\_SIG, CE=>CE\_SIG, ADDR => ADDR\_BUS, CAT CONTROL=>CAT CONTROL);

MEM5 INST 0: MEM5 port map (ADDR=> ADDR BUS, LED OUT=>LEDS);

FSM\_INST\_0: FSM port map (

CLK => CLK,

CLK\_DIV => CE\_SIG,

ARM => ARM,

FRONT\_DOOR => FRONT\_DOOR,

REAR\_DOOR => REAR\_DOOR,

WINDOW => WINDOW,

RUN\_TIMER => RUN\_SIG,

SIREN => SIREN);

#### SECURITY Architecture Syntax Summary

architecture RTL of SECURITY is

component FSM ... component CLK\_DIV ... component MEM5 ... component ADDR\_CNTRwCAT ... component INDICATORS ...

```

signal CE_SIG: std_logic;

signal ADDR_BUS: std_logic_vector(4 downto 0);

signal RUN SIG: std logic;

```

#### Begin

```

INDICATORS_INST_0: ...

CLK_DIV_INST_0: ...

ADDR_CNTRwCAT_INST_0: ...

MEM5_INST_0: ...

FSM_INST_0: ...

```

end architecture RTL;

## Hands-on (30 minutes)

Step 1 / Lab procedure Creating the Top-Level Module SECURITY.vhd using Xilinx ISE (see sample screen shot)

#### Finite State Machine Module: FSM.vhd

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

#### entity FSM is

Port ( CLK : in STD\_LOGIC; CLK\_DIV:in STD\_LOGIC; ARM : in STD\_LOGIC; FRONT\_DOOR : in STD\_LOGIC; REAR\_DOOR : in STD\_LOGIC; WINDOW : in STD\_LOGIC; RUN\_TIMER:out STD\_LOGIC; SIREN : out STD\_LOGIC);

end FSM;

architecture Behavioral of FSM is

type SECURITY\_STATE is (ARMED, DISARMED, WAIT\_DELAY, ALARM);

signal CURR STATE, NEXT STATE: SECURITY STATE;

signal START\_COUNT,COUNT\_DONE: std\_logic;

signal SENSORS:std\_logic\_vector (2 downto 0); --combine inputs

signal TIMER CNTR: std logic vector (2 downto 0) := (others => '0');

### FSM / SYNC process

Begin

SENSORS <= FRONT\_DOOR & REAR\_DOOR & WINDOW; -- &: concatenate

SYNC: process (CLK, ARM)

begin

end process SYNC;

```

STATE MACHINE: process (CURR STATE, SENSORS, ARM, COUNT DONE)

begin

START COUNT <= '0'; -- establish default</pre>

case (CURR STATE) is

when DISARMED =>

if ARM = '1' then

NEXT STATE <= ARMED;

else NEXT STATE <= DISARMED;

end if;

-- Output:

SIREN <= '0';

RUN TIMER <= '0';

when ARMED =>

if (SENSORS /= "000") then

NEXT STATE <= WAIT DELAY;

else NEXT STATE <= ARMED;

end if;

-- Output:

SIREN <= '0';

RUN TIMER <= '0';

when WAIT DELAY =>

START COUNT <= '1';

if (COUNT DONE = '1') then

NEXT STATE <= ALARM;

elsif (ARM ='0') then

NEXT STATE <= DISARMED;

else NEXT STATE <= WAIT DELAY;

end if;

-- Output:

SIREN <= '0';

RUN TIMER <= '1';

when ALARM =>

if (ARM = '0') then

NEXT STATE <= DISARMED;

else NEXT STATE <= ALARM;

end if;

-- Output:

SIREN <= '1';

RUN TIMER <= '0';

end case;

end process STATE MACHINE;

```

#### DELAY\_TIMER process

DELAY TIMER: process (CLK DIV, CURR STATE, START COUNT, TIMER CNTR)

#### begin

```

COUNT_DONE <= '0'; -- default value

if (rising_edge (CLK_DIV) and (START_COUNT = '1')) then

TIMER_CNTR <= TIMER_CNTR + 1;

end if; --rising_edge (CLK_DIV)

if (CURR_STATE/=WAIT_DELAY) then -- /= : NOT equal

TIMER_CNTR <= "000";

end if;

if (TIMER_CNTR = "111") then

COUNT_DONE <= '1';</pre>

```

end if;

end process DELAY\_TIMER;

#### FSM.vhd Syntax Summary

library IEEE; use IEEE.STD LOGIC 1164.ALL; use IEEE.STD LOGIC ARITH.ALL; use IEEE.STD LOGIC UNSIGNED.ALL; entity FSM is Port ( ... ); end FSM; architecture Behavioral of FSM is type ... signal ... Begin SYNC: process ... STATE MACHINE: process ...

DELAY TIMER: process ...

end Behavioral;

# Hands-on (30 minutes)

Step 2 / Lab Procedure Create FSM.vhd using Xilinx ISE (see sample screen shot)

# Hands-on (30 minutes)

Step 3 / Lab Procedure Implementing and Downloading the Design to Spartan 3E

# Hands-on (15 minutes)

Step 4 / Lab Procedure System Verification

# Hands-on (Bonus Round)

Step 5: (Bonus Round)

If time is available, modify the source files to reflect the following new system requirements:

- The REAR\_DOOR sensor is replaced by FIRE sensor.

- A new output SPRINKLER is created to control a sprinkler system.

In addition to the previous requirements, when FIRE is detected, Siren and Sprinkler system are activated immediately without time delay.

### **Resource for Instructors**

(Resources will be available for Summer 2010 FPGA Workshop)

SECURITY.vhd (Top-Level module that ties the following sub modules together)

FSM.vhd (Security State Machine)

INDICATORS.vhd (Spartan 3E Onboard LED Indicators)

CLK\_DIV.vhd (Divide system clock from 50 MHz to 1.49 Hz for timer display)

ADDR\_CNTRwCAT.vhd (Address Counter with scan signal for 7-segment LEDs)

MEM5.vhd (Memory for 2-digit 7-segment LED display)

SECURITY.ucf (I/O Assignments for Spartan 3E demo board)

## Contrast TTL vs VHDL Experiment

| TTL                                                                                     | VHDL/ISE Project Navigator                                               |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Method                                                                                  | Method                                                                   |

| Create State Excitation & Transition Table                                              | Create Process using Hardware Description Language                       |

| <ul> <li>Karnaugh Map for simplification</li> </ul>                                     | Using Synthesize tool                                                    |

| <ul> <li>Create schematics from design equations</li> </ul>                             | Using Implement design tool                                              |

| Implementation                                                                          | Implementation                                                           |

| TTL breadboard                                                                          | <ul> <li>Download to target board using ISE Project Navigator</li> </ul> |

| Time                                                                                    | Time                                                                     |

| <ul> <li>8 hours (including trouble shooting for wiring connections problem)</li> </ul> | • 2 hours                                                                |

| Complexity                                                                              | Complexity                                                               |

| <ul> <li>Limited (Karnaugh map gets complicated<br/>after 4 variables)</li> </ul>       | • open                                                                   |

###

Sec.

# **Questions?**

# VHDL/FPGA Workshop

High Tech Workforce Initiative

- Plan a workshop for Summer 2011.

- The workshop will be provided by NSF. Each participant will receive stipend for travel and lodging.

- If you are interested please email Bassam Matar at:

b.matar@cgcmail.maricopa.edu

###

Sec.

# **Questions?**

# Help us become better

HTWI

High Tech Workforce Initiative

Please complete this quick 1 minute survey to help us become better and to let us know what webinars you would like to see in the future.

http://www.questionpro.com/t/ABkVkZIOXa

# Webinar Recordings

HTWI

High Tech Workforce Initiative

To access this recording, visit *www.matecnetworks.org*, Keyword Search: "webinar HTWI FPGA"

## **HTWI Upcoming Webinars**

ΗΤ

High Tech Workforce Initiative

**December 3:** Supply Chain and Inventory Control: Limiting Factors and the Technologies That Help Them Work

Visit *www.matecnetworks.org* for more details about these and other upcoming webinars.

# NetWorks Upcoming Webinars HTWI

October 8: Innovative STEM Resources November 12: Electronics Education Today

Visit **www.matecnetworks.org** for more details about these and other upcoming webinars.

Thank you for attending Field Programmable Gate Array (FPGA) Curriculum update with Industry

Hosted by MATEC NetWorks

Funded, in part by a grant from the National Science Foundation DUE 1003542